在半导体封装过程中,蚀刻和材料选择对封装阻抗控制有着重要的影响。蚀刻过程可以调整封装材料的形状和几何结构,从而改变器件的尺寸和电性能。材料选择则决定了封装材料的电学特性,包括介电常数和导电性等。

蚀刻对阻抗的影响主要通过改变电磁场和电流的分布来实现。通过控制蚀刻参数,如蚀刻深度、蚀刻速率和蚀刻剂的组成,可以调整封装材料的几何形状和厚度,从而影响器件的阻抗特性。例如,通过蚀刻可以实现更窄的线宽和间距,从而降低线路的阻抗。

材料选择对阻抗的影响主要体现在材料的介电常数和导电性上。不同的封装材料具有不同的介电常数,介电常数的不同会导致信号的传播速度和阻抗发生变化。此外,选择具有适当导电性的封装材料可以提供更低的电阻和更好的信号传输性能。

因此,研究蚀刻和材料选择对半导体封装阻抗控制的关系可以帮助优化封装过程,提高封装器件的性能和可靠性。这对于半导体行业来说是非常重要的,可以为开发和制造高性能的半导体器件提供亚博安卓的技术支持。探索蚀刻技术对半导体封装的影响力!黑龙江半导体封装载体技术规范

在半导体封装中,蚀刻技术可以用于实现微米甚至更小尺寸的结构和器件制备。以下是一些常见的尺寸制备策略:

1. 基础蚀刻:基础蚀刻是一种常见的尺寸制备策略,通过选择合适的蚀刻剂和蚀刻条件,可以在半导体材料上进行直接的蚀刻,从而形成所需的结构和尺寸。这种方法可以实现直接、简单和高效的尺寸制备。

2. 掩蔽蚀刻:掩蔽蚀刻是一种利用掩膜技术进行尺寸制备的策略。首先,在待蚀刻的半导体材料上覆盖一层掩膜,然后通过选择合适的蚀刻剂和蚀刻条件,在掩膜上进行蚀刻,从而将所需的结构和尺寸转移到半导体材料上。这种方法可以实现更加精确和可控的尺寸制备。

3. 镀膜与蚀刻:镀膜与蚀刻是一种常见的尺寸制备策略,适用于需要更高精度的尺寸制备。首先,在待蚀刻的半导体材料上进行一层或多层的镀膜,然后通过选择合适的蚀刻剂和蚀刻条件,来蚀刻镀膜,从而得到所需的结构和尺寸。这种方法可以通过控制镀膜的厚度和蚀刻的条件,实现非常精确的尺寸制备。

总的来说,蚀刻技术在半导体封装中可以通过基础蚀刻、掩蔽蚀刻和镀膜与蚀刻等策略来实现尺寸制备。选择合适的蚀刻剂和蚀刻条件,结合掩膜技术和镀膜工艺,可以实现不同尺寸的结构和器件制备,满足不同应用需求。山西半导体封装载体市场半导体封装技术的基本原理。

使用蚀刻工艺可以提升半导体封装的质量与可靠性的方法有以下几个方面:

优化蚀刻工艺参数:在进行蚀刻过程中,合理选择刻蚀液的成分、浓度、温度、时间等参数,以及控制刻蚀液的流速和搅拌方式,可以有效提高蚀刻的均匀性和准确性,从而提升封装的质量。通过实验和模拟优化工艺参数,可以获得更好的蚀刻效果。

表面预处理:在进行蚀刻之前,对待刻蚀的表面进行适当的预处理,如清洗、去除氧化层等,以确保目标材料表面的纯净性和一致性。这样可以避免蚀刻过程中出现不均匀的刻蚀和不良的质量。

控制蚀刻深度和侵蚀率:蚀刻的深度和侵蚀率是影响封装质量和可靠性的重要因素。通过精确控制蚀刻时间、浓度和波动等参数,可以实现准确控制蚀刻深度,并避免过度蚀刻或局部侵蚀。这可以确保封装器件的尺寸和形状符合设计要求,并提高可靠性。

监控蚀刻过程:在蚀刻过程中,通过实时监测和记录蚀刻深度、表面形貌和刻蚀速率等关键参数,可以及时发现蚀刻过程中的异常情况,避免不良的蚀刻现象。这有助于提高封装的质量并保证一致性。

综合考虑材料特性、工艺要求和设备条件等因素,选择合适的蚀刻方法和优化工艺参数,可以有效提升半导体封装的质量与可靠性。

蚀刻技术在半导体封装中用于调控微观结构是非常重要的。下面是一些常用的微观结构调控方法:

蚀刻选择性:蚀刻选择性是指在蚀刻过程中选择性地去除特定的材料。通过调整蚀刻液的成分、浓度、温度和时间等参数,可以实现对特定材料的选择性蚀刻。这样可以在半导体封装中实现微观结构的调控,如开孔、通孔和刻蚀坑等。

掩模技术:掩模技术是通过在待蚀刻的表面上覆盖一层掩膜或掩膜图案来控制蚀刻区域。掩膜可以是光刻胶、金属膜或其他材料。通过光刻工艺制备精细的掩膜图案,可以实现对微观结构的精确定位和形状控制。

物理辅助蚀刻技术:物理辅助蚀刻技术是指在蚀刻过程中通过物理机制来辅助蚀刻过程,从而实现微观结构的调控。例如,通过施加外加电场、磁场或机械力,可以改变蚀刻动力学,达到所需的结构调控效果。

温度控制:蚀刻过程中的温度控制也是微观结构调控的重要因素。通过调整蚀刻液的温度,可以影响蚀刻动力学和表面反应速率,从而实现微观结构的调控。

需要注意的是,在进行微观结构调控时,需要综合考虑多种因素,如蚀刻液的成分和浓度、蚀刻时间、温度、压力等。同时,还需要对蚀刻过程进行严密的控制和监测,以确保所得到的微观结构符合预期要求。封装技术对半导体芯片的保护和信号传输的重要性。

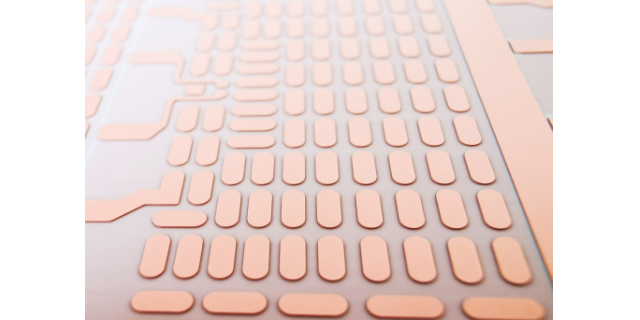

基于蚀刻技术的高密度半导体封装器件设计与优化涉及到以下几个方面:

1. 设计:首先需要进行器件的设计,包括电路布局、层次结构和尺寸等。设计过程中考虑到高密度封装的要求,需要尽量减小器件尺寸,提高器件的集成度。

2. 材料选择:选择合适的材料对器件性能至关重要。需要考虑材料的导电性、导热性、抗腐蚀性等性能,以及与蚀刻工艺的配合情况。

3. 蚀刻工艺:蚀刻技术是半导体器件制备过程中的关键步骤。需要选择合适的蚀刻剂和工艺参数,使得器件的图案能够得到良好的加工。

4. 优化:通过模拟和实验,对设计的器件进行优化,以使其性能达到较好状态。优化的主要目标包括减小电阻、提高导电性和降低功耗等。

5. 封装和测试:设计和优化完成后,需要对器件进行封装和测试。封装工艺需要考虑器件的密封性和散热性,以保证器件的可靠性和工作稳定性。

总的来说,基于蚀刻技术的高密度半导体封装器件设计与优化需要综合考虑器件设计、材料选择、蚀刻工艺、优化和封装等方面的问题,以达到高集成度、高性能和高可靠性的要求。探索半导体封装技术的发展趋势。黑龙江半导体封装载体技术规范

蚀刻技术如何实现半导体芯片的多层结构!黑龙江半导体封装载体技术规范

界面蚀刻是一种在半导体封装中有着广泛应用潜力的技术。

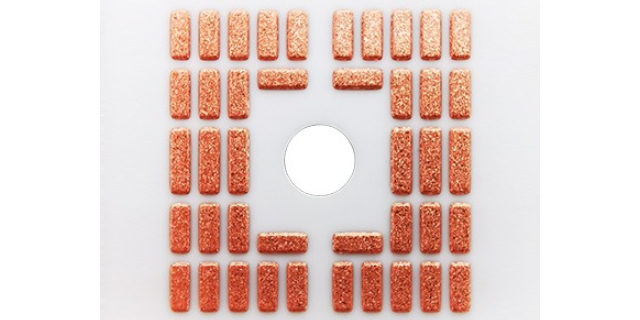

封装层间连接:界面蚀刻可以被用来创建精确的封装层间连接。通过控制蚀刻深度和形状,可以在封装层间创建微小孔洞或凹槽,用于实现电气或光学连接。这样的层间连接可以用于高密度集成电路的封装,提高封装效率和性能。

波导制作:界面蚀刻可以被用来制作微细波导,用于光电器件中的光传输或集装。通过控制蚀刻参数,可以在半导体材料上创建具有特定尺寸和形状的波导结构,实现光信号的传输和调制。

微尺度传感器:界面蚀刻可以被用来制作微尺度传感器,用于检测温度、压力、湿度等物理和化学量。通过控制蚀刻参数,可以在半导体材料上创建微小的敏感区域,用于感测外部环境变化,并将其转化为电信号。

三维系统封装:界面蚀刻可以被用来创建复杂的三维系统封装结构。通过蚀刻不同材料的层,可以实现器件之间的垂直堆叠和连接,提高封装密度和性能。

光子集成电路:界面蚀刻可以与其他光刻和蚀刻技术结合使用,用于制作光子集成电路中的光学器件和波导结构。通过控制蚀刻参数,可以在半导体材料上创建微小的光学器件,如波导耦合器和分光器等。黑龙江半导体封装载体技术规范